## **UNIT I BASIC STRUCTURE OF COMPUTERS**

**Functional units – Basic operational concepts** – Bus Structures – Performance – Memory locations and addresses – Memory operations – Instruction and Instruction sequencing –– Addressing modes – Assembly language – Case study : RISC and CISC Architecture.

# Recall the previous class concepts

**Angel Latha Mary S**

2

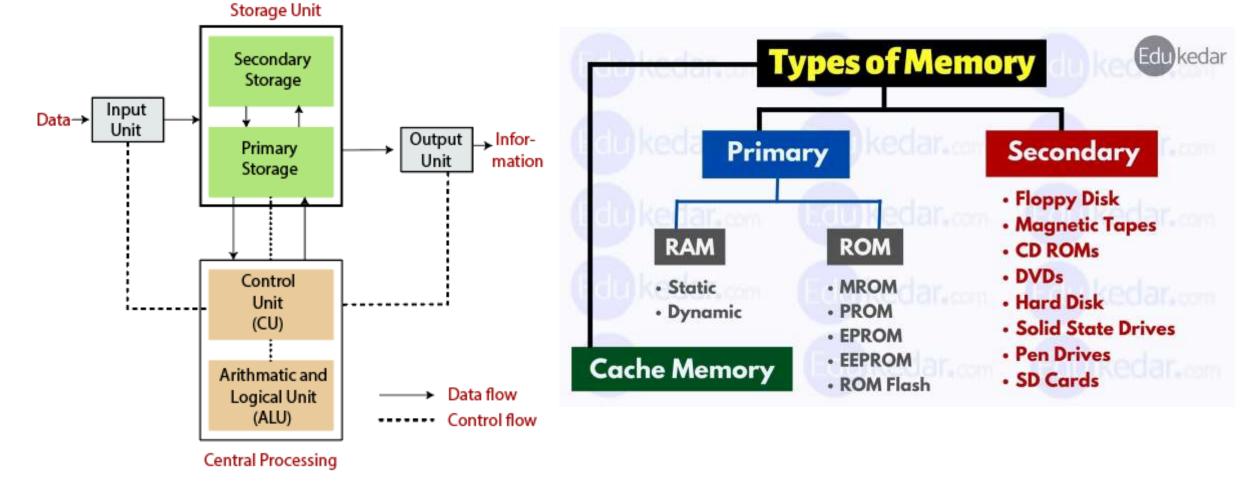

Block diagram of Computer

INSTITUTIONS

#### **Functional Unit**

**Angel Latha Mary S**

3

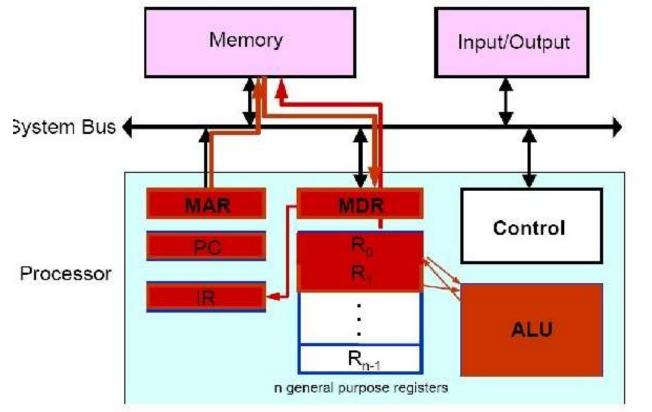

### Analysing how processor and memory are connected

- Processors have various registers to perform various functions

- **Program Counter** It contains the memory address of next instruction to be fetched.

- Instruction Register It holds the instruction which is currently being executed

- **MDR** It facilities communication with memory. It contains the data to be written into or read out of the addressed location.

- MAR It holds the address of the location that is to be accessed n general purpose registers that is R0 to Rn-1

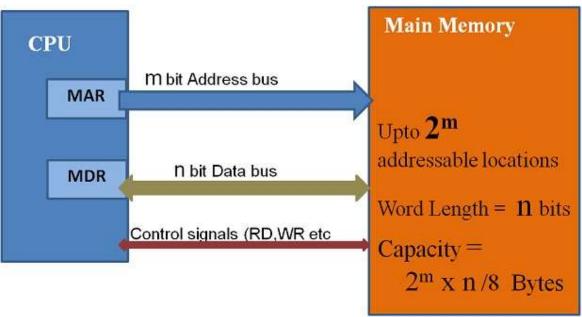

#### **Example A Connection between Processor** & Memory

5/14

#### **Operations & Operands -**

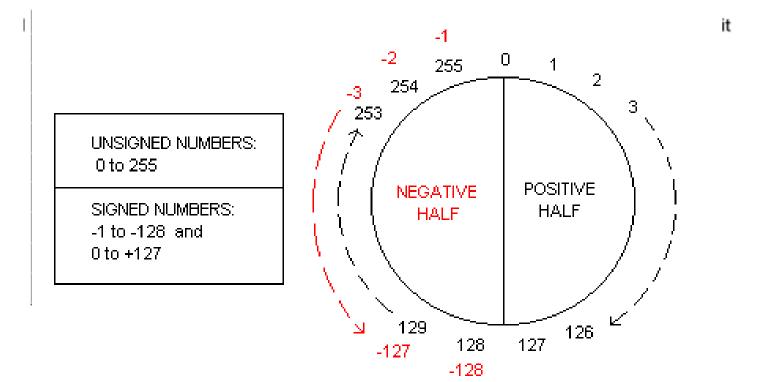

8-BIT NUMBER SYSTEM

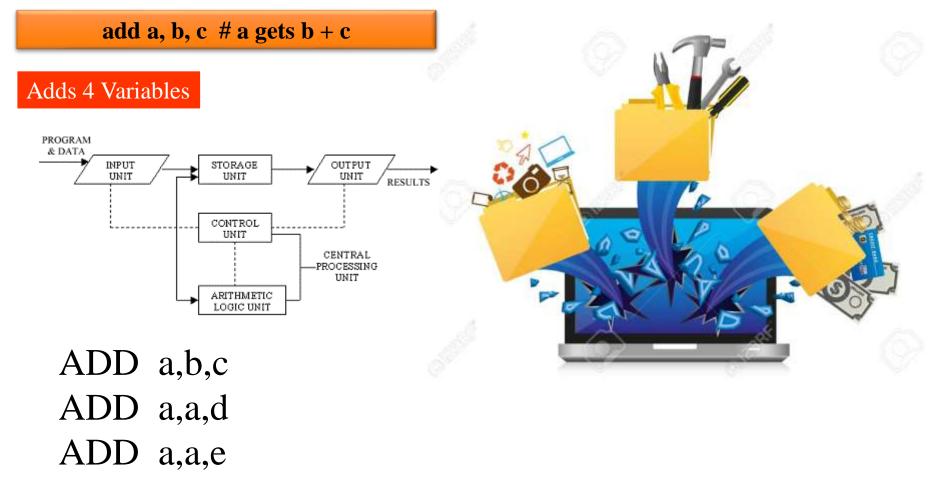

#### **Operations of Computer Hardware**

#### **Basic Operational Concepts**

• Instruction consists of 2 parts

• Example

ADD LOCA, RO

Load LOCA, R1 Add R1, R0

Angel Latha Mary S

8

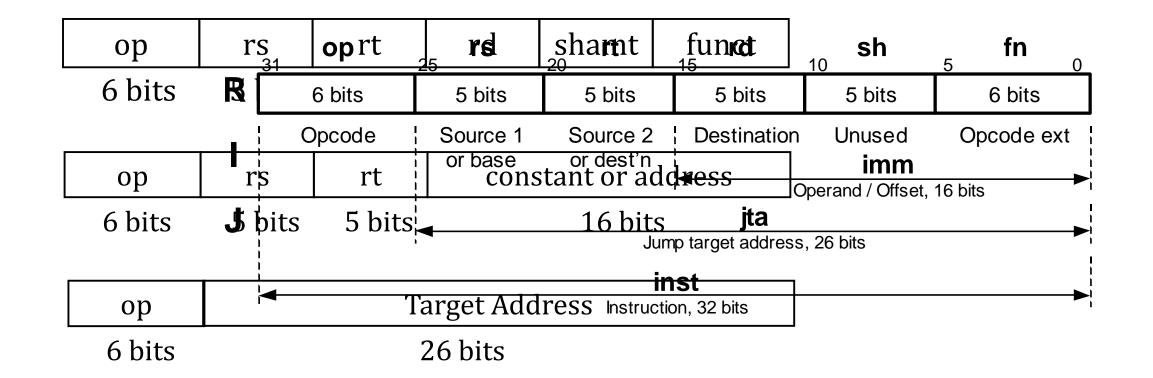

#### **Instructions Format**

#### **Translating Arm Assembly Instructions into Machine Instructions**

| [ | op<br>6 bits |   |    | rt<br>5 bits | rd<br>5 bits | sham<br>5 bits |       |       | add \$ | t0, \$s1, \$s2 |

|---|--------------|---|----|--------------|--------------|----------------|-------|-------|--------|----------------|

|   |              | [ | sp | ecial        | \$s1         | \$s2           | \$t0  | 0     | add    | ]              |

|   |              |   |    | 0            | 17           | 18             | 8     | 0     | 32     | ]              |

|   |              |   | 00 | 0000         | 10001        | 10010          | 01000 | 00000 | 100000 | ]              |

$00000100011001001000000010000_2 = 02324020_{16}$

Angel Latha Mary S

10/14

#### **ARM Assembly Language**

|   | Logical               | and                                 | and \$\$1,\$\$2,\$\$3 | \$s1 = \$s2 & \$s3                                         |        |

|---|-----------------------|-------------------------------------|-----------------------|------------------------------------------------------------|--------|

|   |                       | or                                  | or \$s1,\$s2,\$s3     | \$s1 = \$s2   \$s3                                         |        |

|   |                       | nor                                 | nor \$s1,\$s2,\$s3    | \$s1 = ~ (\$s2   \$s3)                                     |        |

|   |                       | and immediate                       | andi \$s1,\$s2,20     | \$s1 = \$s2 & 20                                           |        |

| 1 |                       | or immediate                        | ori \$s1,\$s2,20      | \$s1 = \$s2   20                                           |        |

|   |                       | shift left logical                  | sll \$s1,\$s2,10      | \$s1 = \$s2 << 10                                          |        |

| ĺ |                       | shift right logical                 | srl \$s1,\$s2,10      | \$s1 = \$s2 >> 10                                          |        |

|   | Conditional<br>branch | branch on equal                     | beq \$s1.\$s2.25      | if (\$s1 == \$s2) go to<br>PC + 4 + 100                    |        |

|   |                       | branch on not equal                 | bne \$s1,\$s2,25      | if (\$s1!= \$s2) go to<br>PC + 4 + 100                     |        |

|   |                       | set on less than                    | slt \$s1,\$s2,\$s3    | <pre>if (\$s2 &lt; \$s3) \$s1 = 1;<br/>else \$s1 = 0</pre> |        |

| t |                       | set on less than<br>unsigned        | sltu \$s1,\$s2,\$s3   | <pre>if (\$s2 &lt; \$s3) \$s1 = 1;<br/>else \$s1 = 0</pre> |        |

|   |                       | set less than immediate             | slti \$s1,\$s2,20     | if (\$s2 < 20) \$s1 = 1;<br>else \$s1 = 0                  |        |

|   |                       | set less than<br>immediate unsigned | sltiu \$s1,\$s2,20    | If (\$s2 < 20) \$s1 = 1;<br>else \$s1 = 0                  | 0 or 1 |

| · | Unconditional jump    | jump                                | j 2500                | go to 10000                                                |        |

|   |                       | jump register                       | jr \$ra               | go to \$ra                                                 |        |

| - |                       | jump and link                       | jal 2500              | \$ra = PC + 4; go to 10000                                 |        |

INSTITUTIONS

#### **Operating System**