# SNS COLLEGE OF TECHNOLOGY

(An Autonomous Institution) Coimbatore – 641 035.

## B.E / B.Tech – Internal Assessment Exam- II Academic Year 2023-2024 (ODD) FIFTH SEMESTER (REGULATION R2019)

**19ITT202 – COMPUTER ORGANIZATION AND ARCHITECTURE**

## TIME: 1.5 HOURS

#### MAXIMUM MARKS: 50

# **ANSWER ALL QUESTIONS**

| $\underline{PART A - (5 x 2 = 10 Marks)}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |       |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--|--|

| 1.                                        | <ul><li>What are the rules to perform addition on floating point numbers?</li><li>1. Choose the number with the smaller exponent and shift its mantissa right a number of steps equal to the difference in exponents.</li><li>2. Set the exponent of the result equal to the larger exponent.</li><li>3. Perform addition/subtraction on the mantissas and determine the sign of the result.</li><li>4. Normalize the resulting value, if necessary.</li></ul>                       | CO2 | UND   |  |  |

| 2.                                        | Subtract (11010) <sub>2</sub> -(10000) <sub>2</sub> using 1's complement and 2's complement<br>method.<br>1s complement-> 01001<br>2s complement -> 01010                                                                                                                                                                                                                                                                                                                            | CO2 | APP   |  |  |

| 3.                                        | Mention the various phase of an executing an instruction.<br>fetching an instruction from memory, decoding the fetched instruction,<br>reading the address from memory, and finally, instruction execution                                                                                                                                                                                                                                                                           | CO3 | REM   |  |  |

| 4.                                        | What are steps required to execute an instruction by the processor?<br>An instruction is executed by performing one or more of the<br>following operations: 1) Transfer a word of data from one register to<br>another or to the ALU. 2) Perform arithmetic or a logic operation and<br>store the result in a register. 3) Fetch the contents of a given memory-<br>location and load them into a register. 4) Store a word of data from a<br>register into a given memory-location. | CO3 | UND   |  |  |

| 5.                                        | Write the sequence of operations to perform the Instruction [R3]<-<br>[R1]+[R2]<br>1. R1out, Yin<br>2. R2out, SelectY, Add, Zin<br>3. Zout, R3in                                                                                                                                                                                                                                                                                                                                     | CO3 | UND   |  |  |

| 6. (8                                     | PART- B (2 x 13 = 26 Marks , 1*14=14 Marks<br>a) Perform the arithmetic operations below with binary numbers and with neg                                                                                                                                                                                                                                                                                                                                                            |     | 1 CO2 |  |  |

| 6. | (a) | Perform the arithmetic operations below with binary numbers and with negative       | 1 | CO <sub>2</sub> | APP |

|----|-----|-------------------------------------------------------------------------------------|---|-----------------|-----|

|    |     | numbers in signed 2's complement representation. Use seven bits to accommodate      | 3 |                 |     |

|    |     | each number together with its sign. In each case, determine if there is an overflow |   |                 |     |

|    |     | by checking the carries into and out of the sign bit position.                      |   |                 |     |

|    |     | a. (+35) + (+40)                                                                    |   |                 |     |

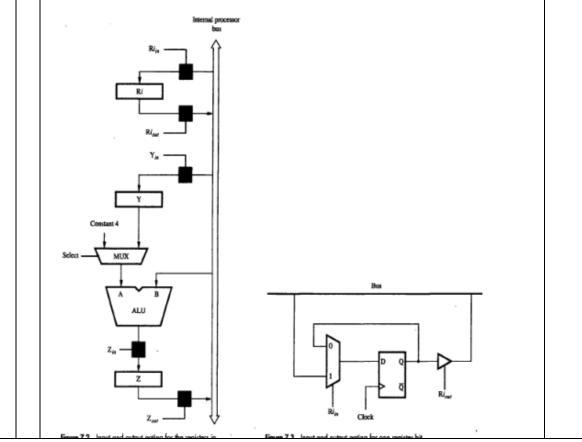

control-signals to all the units inside the processor. We implement the actions specified by the instruction (loaded in the IR). Register R0 through R(n-1) are the Processor Registers. The programmer can access these registers for general-purpose use. Only processor can access 3 registers Y, Z & Temp for temporary storage during program-execution. The programmer cannot access these 3 registers. In ALU,1) "A" input gets the operand from the output of the multiplexer (MUX). 2) "B" input gets the operand directly from the processor-bus. There are 2 options provided for "A" input of the ALU. MUX is used to select one of the 2 inputs. MUX selects either output of Y or constant-value 4( which is used to increment PC content).

Disadvantage: Only one data-word can be transferred over the bus in a clock cycle. Solution: Provide multiple internal-paths. Multiple paths allow several data-transfers to take place in parallel.

#### **REGISTER TRANSFERS**

Instruction execution involves a sequence of steps in which data are transferred from one register to another. For each register, two control-signals are used: Riin & Riout. These are called Gating Signals. Riin=1 = data on bus is loaded into Ri. Riout=1 as content of Ri is placed on bus. Riout=0, makes bus can be used for transferring data from other registers.For example, Move R1, R2; This transfers the contents of register R1 to register R2. This can be accomplished as follows: 1) Enable the output of registers R1 by setting R1out to 1 (Figure 7.2). This places the contents of R1 on processor-bus. 2) Enable the input of register R2 by setting R2out to 1. This loads data from processor-bus into register R4.

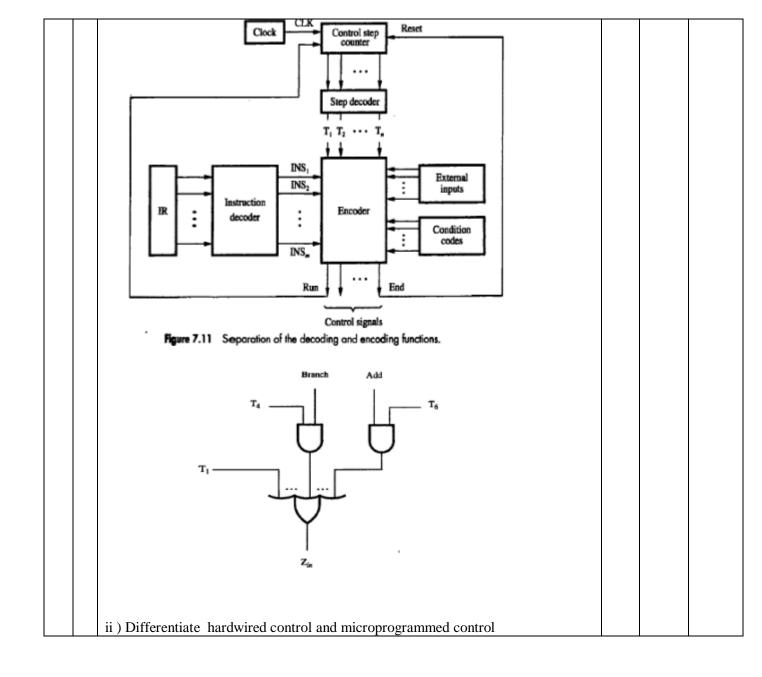

| 7. | (a) | <ul> <li>i) Discuss about hardwired control<br/>Hardwired control is a method of control unit design (Figure). The control-<br/>signals are generated by using logic circuits such as gates, flip-flops, decoders<br/>etc. Decoder / Encoder Block is a combinational-circuit that generates<br/>required control-outputs depending on state of all its inputs. Instruction<br/>decoder decodes the instruction loaded in the IR. If IR is an 8 bit register,<br/>then instruction decoder generates 28(256 lines); one for each instruction. It<br/>consists of a separate output-lines INS1 through INSm for each machine<br/>instruction. According to code in the IR, one of the output-lines INS1 through<br/>INSm is set to 1, and all other lines are set to 0. Step-Decoder provides a<br/>separate signal line for each step in the control sequence. Encoder gets the<br/>input from instruction decoder, step decoder, external inputs and condition<br/>codes. It uses all these inputs to generate individual control-signals: Yin,<br/>PCout, Add, End and so on. For example (Figure 7.12),<br/>Zin=T1+T6.ADD+T4.BR; This signal is asserted during time-slot T1 for all<br/>instructions during T6 for an Add instruction. During T4 for unconditional<br/>branch instruction, when RUN=1, counter is incremented by 1 at the end of<br/>every clock cycle. When RUN=0, counter stops counting. After execution of<br/>each instruction, end signal is generated. End signal resets step counter.<br/>Sequence of operations carried out by this machine is determined by wiring<br/>of logic circuits, hence the name "hardwired". Advantage: Can operate at<br/>high speed.</li> <li>Disadvantages: 1) Since no. of instructions/control-lines is often in<br/>hundreds, the complexity of control unit is inflexible because it is difficult to<br/>change the design.</li> </ul> | 7 | CO3 | UND |

|----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|

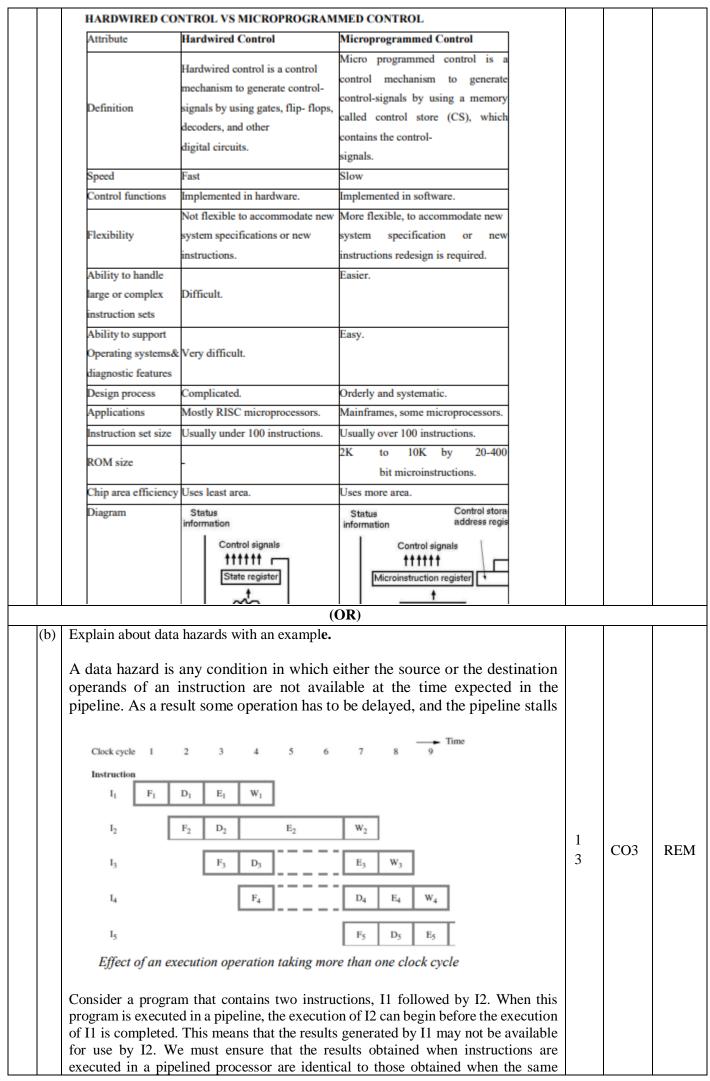

instructions are executed sequentially. The potential for obtaining incorrect results when operations are performed concurrently can be demonstrated by a simple example. Assume that A=5, and consider the following two operations:  $A \leftarrow 3 + A$

$B \leftarrow 4 \times A$

When these operations are performed in the order given, the result is B = 32. But if they are performed concurrently, the value of A used in computing B would be the original value, 5, leading to an incorrect result. If these two operations are performed by instructions in a program, then the instructions must be executed one after the other, because the data used in the second instruction depend on the result of the first instruction. On the other hand, the two operations  $A \leftarrow 5 \times C$

$B \leftarrow 20 + C$  can be performed concurrently, because these operations are independent.

This example illustrates a basic constraint that must be enforced to guarantee correct results. When two operations depend on each other, they must be performed sequentially in the correct order. This rather obvious condition has far-reaching consequences. Understanding its implications is the key to understanding the variety of design alternatives and trade-offs encountered in pipelined computers. Consider the pipeline in Figure 2. The data dependency just described arises when the destination of one instruction is used as a source in the next instruction.

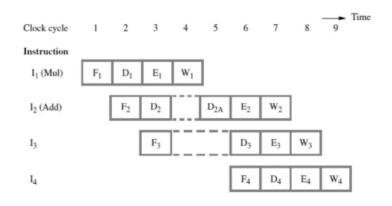

For example, the two instructions Mul R2,R3,R4 Add R5,R4,R6 give rise to a data dependency. The result of the multiply instruction is placed into register R4, which in turn is one of the two source operands of the Add instruction. Assuming that the multiply operation takes one clock cycle to complete, execution would proceed as shown in Figure.

As the Decode unit decodes the Add instruction in cycle 3, it realizes that R4 is used as a source operand. Hence, the D step of that instruction cannot be completed until the W step of the multiply instruction has been completed. Completion of step D2 must be delayed to clock cycle 5, and is shown as step D2A in the figure. Instruction I3 is fetched in cycle 3, but its decoding must be delayed because step D3 cannot precede D2. Hence, pipelined execution is stalled for two cycles.

#### **Operand Forwarding**

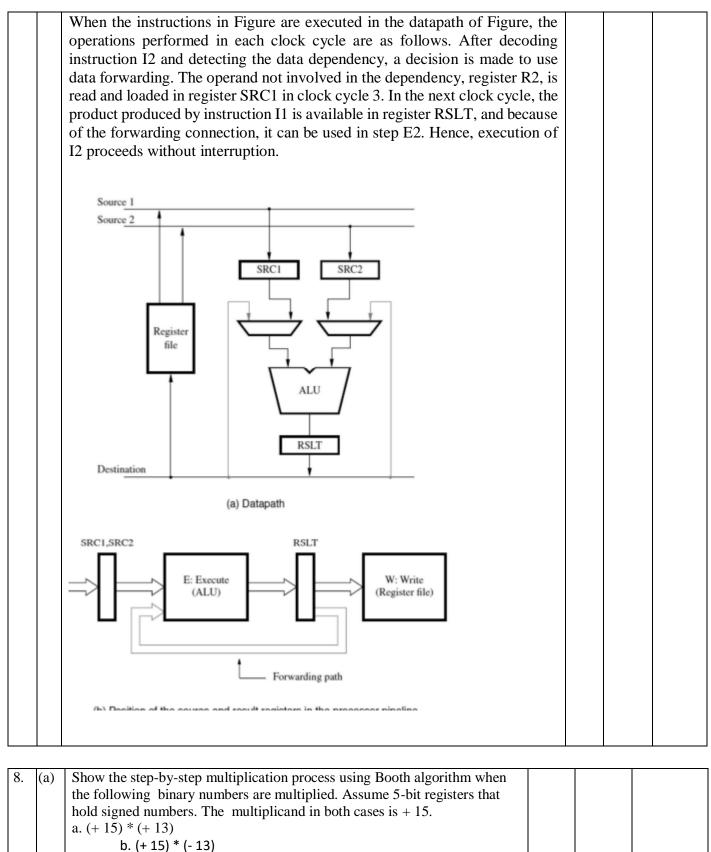

The data hazard just described arises because one instruction, instruction I2 in Figure, is waiting for data to be written in the register file. However, these data are available at the output of the ALU once the Execute stage completes step E1.

Hence, the delay can be reduced, or possibly eliminated, if we arrange for the result of instruction I1 to be forwarded directly for use in step E2. Figure a shows a part of the processor datapath involving the ALU and the register file. This arrangement is similar to the three-bus structure in Figure, except that registers SRC1, SRC2, and RSLT have been added. These registers constitute the interstage buffers needed for pipelined operation, as illustrated in Figure b. With reference to Figure b, registers SRC1 and SRC2 are part of buffer B2 and RSLT is part of B3. The data forwarding mechanism is provided by the blue connection lines. The two multiplexers connected at the inputs to the ALU allow the data on the destination bus to be selected instead of the contents of either the SRC1 or SRC2 register.

|     | b. $(+15) * (-13)$<br>00110 00011<br>+195<br>a.<br>11001 11101<br>b. $-195$                                                                                                                             | 14 | CO2 | APP |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----|

|     | (OR)                                                                                                                                                                                                    |    |     |     |

| (b) | Divide using the restoring and non-restoring division algorithm with step by<br>step intermediate results and explain.<br>(a) 10100011 by 1011 (b) 00001111 by 0011.<br>(Use a dividend of eight bits.) | 14 | CO2 | APP |

| (Sividend) 101000111011 (Sivisos)Restoring. $3^{3}$ cam planent 11110101.Inibately00000000 10100011Shift.00000001Shift.0000001Subtract.11110101State 90 $0^{1}$ 101010State 90 $0^{1}$ 1000011Shift.00000010Shift.00000010Shift.00000010Shift.00000010Shift.000000000Shift.000000000Shift.000000000Shift.000000000Shift.000000000Shift.0000000000Shift.000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |                                                                                                       |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------|--|

| $\begin{array}{c} \text{Tribuleoy} & 0.90000000   0100011 \\ \text{Shift} & 0.0000001   01000111 \\ \text{Subtract} & 1111010101 \\ \text{Set 90} & 010110   01000110 \\ \text{Set 90} & 00000001   01000110 \\ \text{Shift} & 000000000   010000110 \\ \text{Subtrace} & 11110101 \\ \text{Set 90} & 00000000   0000110 \\ \text{Shift} & 000000000   0000110 \\ \text{Shift} & 00000000   0000110 \\ \text{Shift} & 0000000000   0000110 \\ \text{Shift} & 000000000   0000110 \\ \text{Shift} & 000000000   00000000   0000000 \\ \text{Shift} & 00000000   00000000   0000000 \\ \text{Shift} & 000000000   00000000   00000000 \\ \text{Shift} & 000000000   00000000   00000000 \\ \text{Shift} & 000000000   000000000   00000000 \\ \text{Shift} & 000000000   0000000000   000000000   000000$ | • ( Di |                                                                                                       |  |

| Subtract:       11110101         Set 90 $011101010$ Restore:       000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |                                                                                                       |  |

| Restore 1111 1110 Set 90 000 1001 011 EDOPPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        | Subtract:       111110101         Set 90 $011101010$ Restore: $0200000000000000000000000000000000000$ |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6.0    | umbapalayam SSKulam,Tamil Nadu   2023.11.08 16:15                                                     |  |