# SNS COLLEGE OF TECHNOLOGY

(An Autonomous Institution) Coimbatore – 641 035. B.E / B.Tech – Internal Assessment Exam- III Academic Year 2023-2024 (ODD) FIFTH SEMESTER (REGULATION R2019)

### **19ITT202 – COMPUTER ORGANIZATION AND ARCHITECTURE**

#### TIME: 1.5 HOURS

#### MAXIMUM MARKS: 50

#### ANSWER ALL QUESTIONS

| <u>PART A — (5 x 2 = 10 Marks)</u> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |     |  |  |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--|--|

| 1.                                 | Differentiate SRAM from DRAM<br>Static RAMs are fast, but their cells require several transistors. Less<br>expensive and higher density RAMs can be implemented with simpler cells.<br>But, these simpler cells do not retain their state for a long period, unless they<br>are accessed frequently for Read or Write operations. Memories that use such<br>cells are called dynamic RAMs (DRAMs). Information is stored in a dynamic<br>memory cell in the form of a charge on a capacitor, but this charge can be<br>maintained for only tens of milliseconds. | CO4 | UND |  |  |

| 2.                                 | What is memory access time?<br>A useful measure of the speed of memory units is the time that elapses<br>between the initiation of an operation to transfer a word of data and the<br>completion of that operation. This is referred to as the memory access time                                                                                                                                                                                                                                                                                                | CO4 | REM |  |  |

| 3.                                 | Define read hit and write miss.<br>The cache control circuitry determines whether the requested word currently<br>exists in the cache. If it does, the Read or Write operation is performed on<br>the appropriate cache location. In this case, a read or write hit is said to have<br>occurred<br>Write miss occurs in a computer that uses the write-through protocol, the<br>information is written directly into the main memory                                                                                                                             | CO4 | REM |  |  |

| 4.                                 | What is memory mapped I/O?<br>Memory-mapped I/O uses the same address space to address both main<br>memory and I/O devices. The memory and registers of the I/O devices are<br>mapped to (associated with) address values, so a memory address may refer<br>to either a portion of physical RAM or to memory and registers of the I/O<br>device.                                                                                                                                                                                                                 | CO5 | UND |  |  |

| 5. | Mention the difference between subroutine and an Interrupt Subroutine.<br>An important departure from this similarity should be noted. A subroutine<br>performs a function required by the program from which it is called. As<br>such, potential changes to status information and contents of registers are<br>anticipated. However, an interrupt-service routine may not have any relation<br>to the portion of the program being executed at the time the interrupt request<br>is received. Therefore, before starting execution of the interrupt service | CO5 | UND |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|

|    | routine, status information and contents of processor registers that may be<br>altered in unanticipated ways during the execution of that routine must be<br>saved. This saved information must be restored before execution of the<br>interrupted program is resumed. In this way, the original program can<br>continue execution without being affected in any way by the interruption,<br>except for the time delay.                                                                                                                                       |     |     |

# PART- B (2 x 13 = 26 Marks , 1\*14=14 Marks)

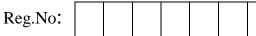

of a computer. Two control lines, R/W and CS, are provided. The R/W (Read/Write) input specifies the required operation, and the CS (Chip Select) input selects a given chip in a multichip memory system. The memory circuit in Figure stores 128 bits and requires 14 external connections for address, data, and control lines. It also needs two lines for power supply and ground connections. Consider now a slightly larger memory circuit, one that has 1K (1024) memory cells. This circuit can be organized as a  $128 \times 8$  memory, requiring a total of 19 external connections. Alternatively, the same number of cells can be organized into a  $1K \times 1$  format. In this case, a 10-bit address is needed, but there is only one data line, resulting in 15 external connections.

## STATIC MEMORIES

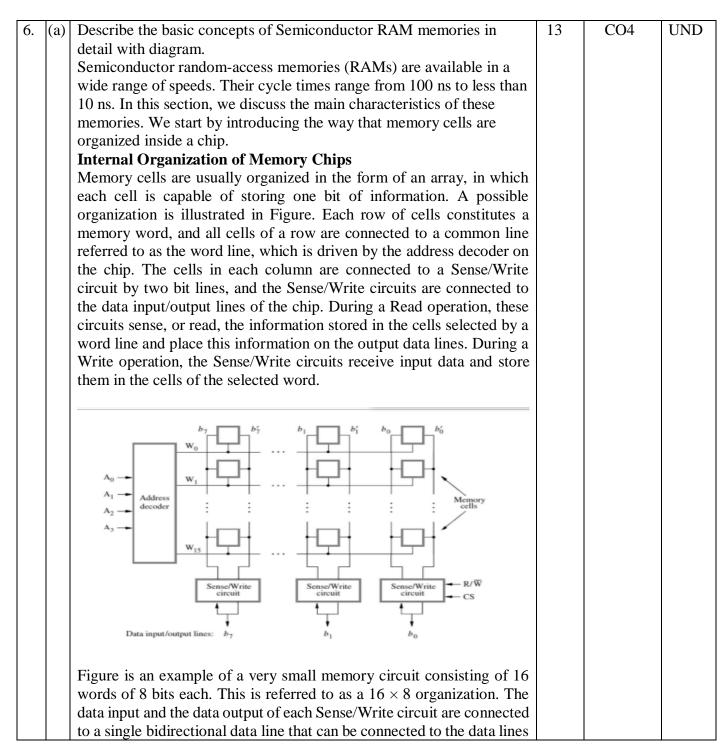

Memories that consist of circuits capable of retaining their state as long as power is applied are known as static memories. Figure illustrates how a static RAM (SRAM) cell may be implemented. Two inverters are cross-connected to form a latch. The latch is connected to two bit lines by transistors T1 and T2. These transistors act as switches that can be opened or closed under control of the word line. When the word line is at ground level, the transistors are turned off and the latch retains its state. For example, if the logic value at point X is 1 and at point Y is 0, this state is maintained as long as the signal on the word line is at ground level. Assume that this state represents the value 1.

## **Read Operation**

In order to read the state of the SRAM cell, the word line is activated to close switches T1 and T2. If the cell is in state 1, the signal on bit line b is high and the signal on bit line b' is low. The opposite is true if the cell is in state 0. Thus, b and b' are always complements of each other. The Sense/Write circuit at the end of the two bit lines monitors their state and sets the corresponding output accordingly.

#### Write Operation

During a Write operation, the Sense/Write circuit drives bit lines b and b', instead of sensing their state. It places the appropriate value on bit line b and its complement on b' and activates the word line. This forces the cell into the corresponding state, which the cell retains when the word line is deactivated.

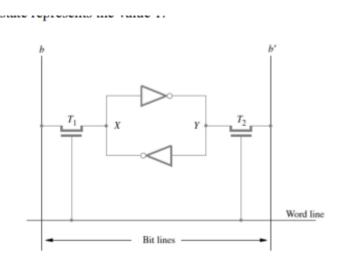

## **CMOS Cell**

A CMOS realization of the cell in Figure is given in Figure. Transistor pairs (T3, T5) and (T4, T6) form the inverters in the latch (see Appendix A). The state of the cell is read or written as just explained.

For example, in state 1, the voltage at point X is maintained high by having transistors T3 and T6 on, while T4 and T5 are off. If T1 and T2 are turned on, bit lines b and bwill have high and low signals, respectively.

Continuous power is needed for the cell to retain its state. If power is interrupted, the cell's contents are lost. When power is restored, the latch settles into a stable state, but not necessarily the same state the cell was in before the interruption. Hence, SRAMs are said to be volatile memories because their contents are lost when power is interrupted. A major advantage of CMOS SRAMs is their very low power consumption, because current flows in the cell only when the cell is being accessed. Otherwise, T1, T2, and one transistor in each inverter are turned off, ensuring that there is no continuous electrical path between Vsupply and ground. Static RAMs can be accessed very quickly. Access times on the order of a few nanoseconds are found in commercially available chips. SRAMs are used in applications where speed is of critical concern.

#### DYNAMIC RAMS

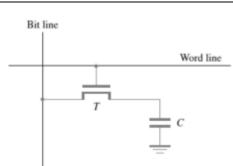

Static RAMs are fast, but their cells require several transistors. Less expensive and higher density RAMs can be implemented with simpler cells. But, these simpler cells do not retain their state for a long period, unless they are accessed frequently for Read or Write operations. Memories that use such cells are called dynamic RAMs (DRAMs). Information is stored in a dynamic memory cell in the form of a charge on a capacitor, but this charge can be maintained for only tens of milliseconds. Since the cell is required to store information for a much longer time, its contents must be periodically refreshed by restoring the capacitor charge to its full value. This occurs when the contents of the cell are read or when new information is written into it. An example of a dynamic memory cell that consists of a capacitor, C, and a transistor, T, is shown in Figure. To store information in this cell, transistor T is turned on and an appropriate voltage is applied to the bit line. This causes a known amount of charge to be stored in the capacitor.

After the transistor is turned off, the charge remains stored in the capacitor, but not for long. The capacitor begins to discharge. This is because the transistor continues to conduct a tiny amount of current, measured in picoamperes, after it is turned off. Hence, the information stored in the cell can be retrieved correctly only if it is read before the charge in the capacitor drops below some threshold value. During a Read operation, the transistor in a selected cell is turned on. A sense amplifier connected to the bit line detects whether the charge stored in the capacitor is above or below the threshold value. If the charge is above the threshold, the sense amplifier drives the bit line to the full voltage representing the logic value 1. As a result, the capacitor is recharged to the full charge corresponding to the logic value 1. If the sense amplifier detects that the charge in the capacitor is below the threshold value, it pulls the bit line to ground level to discharge the capacitor fully. Thus, reading the contents of a cell automatically refreshes its contents. Since the word line is common to all cells in a row, all cells in a selected row are read and refreshed at the same time.

A256-Megabit DRAM chip, configured as  $32M \times 8$ , is shown in Figure. The cells are organized in the form of a  $16K \times 16K$  array. The 16,384 cells in each row are divided into 2,048 groups of 8, forming 2,048 bytes of data. Therefore, 14 address bits are needed to select a row, and another 11 bits are needed to specify a group of 8 bits in the selected row. In total, a 25-bit address is needed to access a byte in this memory. The high-order 14 bits and the loworder 11 bits of the address constitute the row and column addresses of a byte, respectively. To reduce the number of pins needed for external connections, the row and column addresses are multiplexed on 14 pins. During a Read or a Write operation, the row address is applied first. It is loaded into the row address latch in response to a signal pulse on an input control line called the Row Address Strobe (RAS). This causes a Read operation to be initiated, in which all cells in the selected row are read and refreshed.

| -                                                                                                                                                                                                                                                                                                                                                                                                                 | n<br>n<br>n<br>n<br>n<br>n<br>n<br>n<br>n<br>n<br>n<br>n<br>n<br>n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |     |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----|

| control of a second co<br>(CAS). The information<br>group of 8 Sense/Write<br>indicates a Read operate<br>transferred to the da<br>information on theD7-<br>used to overwrite the co<br>8 columns.<br>We should note that in<br>control signals are active<br>these signals change<br>diagrams as RAS and<br>operation of the DRAM<br>CAS signals. These s<br>circuit external to the c<br>command. During a Real | ontrol line called the Column Address laten under<br>ontrol line called the Column Address Strobe<br>on in this latch is decoded and the appropriate<br>e circuits is selected. If the R/W control signal<br>ion, the output values of the selected circuits are<br>ta lines, D7–0. For a Write operation, the<br>0 lines is transferred to the selected circuits, then<br>ontents of the selected cells in the corresponding<br>a commercial DRAM chips, the RAS and CAS<br>we when low. Hence, addresses are latched when<br>from high to low. The signals are shown in<br>CAS to indicate this fact. The timing of the<br><i>A</i> described above is controlled by the RAS and<br>ignals are generated by a memory controller<br>hip when the processor issues a Read or a Write<br>ead operation, the output data are transferred to<br>delay equivalent to the memory's access time.<br><u>(OR)</u> |    |     |     |

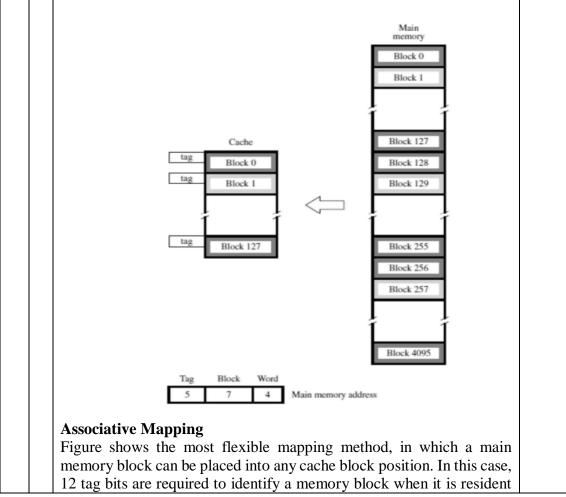

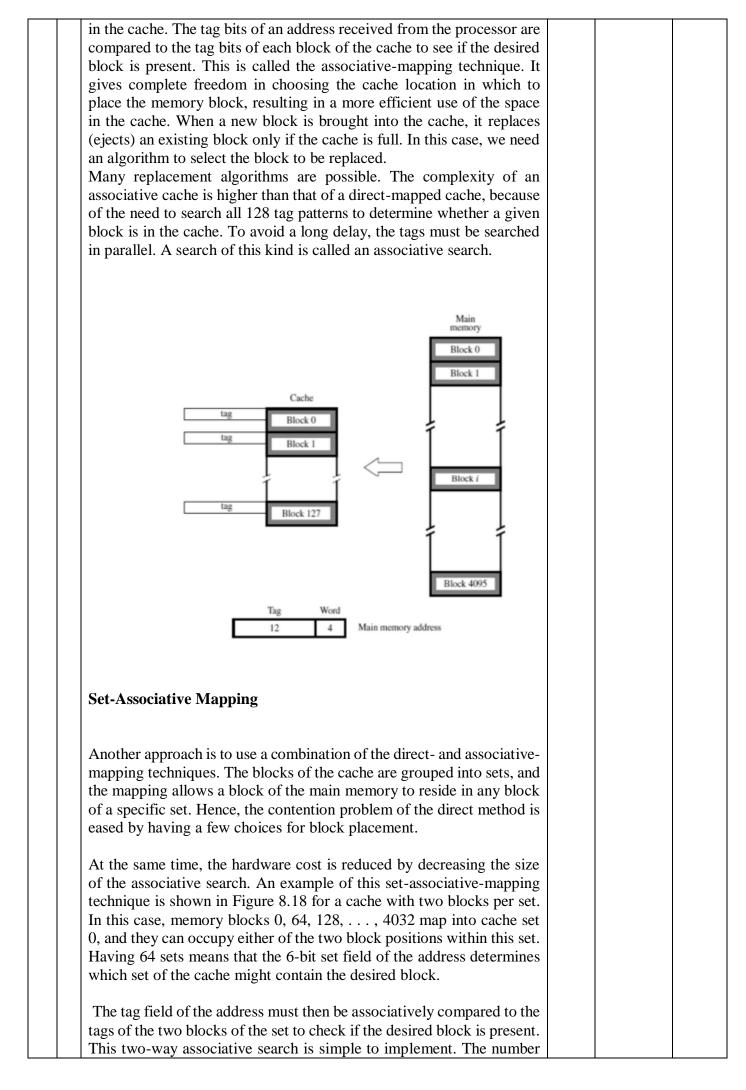

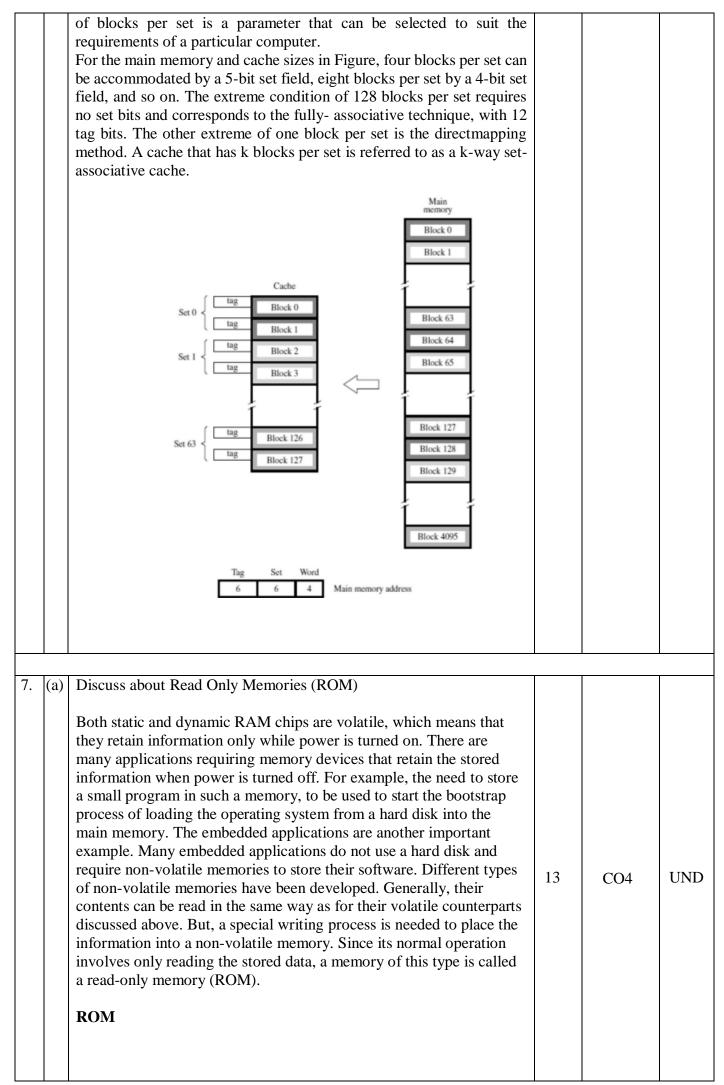

| There are several possiblocks are placed in methods using a specifit 128 blocks of 16 wor assume that the main remain memory has 64K                                                                                                                                                                                                                                                                              | pping schemes used in cache design<br>sible methods for determining where memory<br>the cache. It is instructive to describe these<br>ic small example. Consider a cache consisting of<br>ds each, for a total of 2048 (2K) words, and<br>nemory is addressable by a 16-bit address. The<br>words, which we will view as 4K blocks of 16<br>pplicity, we have assumed that consecutive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13 | CO4 | UND |

The simplest way to determine cache locations in which to store memory blocks is the direct-mapping technique. In this technique, block j of the main memory maps onto block j modulo 128 of the cache, as depicted in Figure. Thus, whenever one of the main memory blocks 0, 128, 256, . . . is loaded into the cache, it is stored in cache block 0. Blocks 1, 129, 257, . . . are stored in cache block 1, and so on. Since more than one memory block is mapped onto a given cache block position, contention may arise for that position even when the cache is not full. For example, instructions of a program may start in block 1 and continue in block 129, possibly after a branch. As this program is executed, both of these blocks must be transferred to the block-1 position in the cache. Contention is resolved by allowing the new block to overwrite the currently resident block.

With direct mapping, the replacement algorithm is trivial. Placement of a block in the cache is determined by its memory address. The memory address can be divided into three fields, as shown in Figure. The low-order 4 bits select one of 16 words in a block. When a new block enters the cache, the 7-bit cache block field determines the cache position in which this block must be stored.

The high-order 5 bits of the memory address of the block are stored in 5 tag bits associated with its location in the cache. The tag bits identify which of the 32 main memory blocks mapped into this cache position is currently resident in the cache. As execution proceeds, the 7-bit cache block field of each address generated by the processor points to a particular block location in the cache.

The high-order 5 bits of the address are compared with the tag bits associated with that cache location. If they match, then the desired word is in that block of the cache. If there is no match, then the block containing the required word must first be read from the main memory and loaded into the cache. The direct-mapping technique is easy to implement, but it is not very flexible.

A memory is called a read-only memory, or ROM, when information can be written into it only once at the time of manufacture. Figure 8.11 shows a possible configuration for a ROM cell. A logic value 0 is stored in the cell if the transistor is connected to ground at point P; otherwise, a 1 is stored. The bit line is connected through a resistor to the power supply. To read the state of the cell, the word line is activated to close the transistor switch.

As a result, the voltage on the bit line drops to near zero if there is a connection between the transistor and ground. If there is no connection to ground, the bit line remains at the high voltage level, indicating a 1. A sense circuit at the end of the bit line generates the proper output value. The state of the connection to ground in each cell is determined when the chip is manufactured, using a mask with a pattern that represents the information to be stored.

### PROM

Some ROM designs allow the data to be loaded by the user, thus providing a programmable ROM (PROM). Programmability is achieved by inserting a fuse at point P, in Figure. Before it is programmed, the memory contains all 0s. The user can insert 1s at the required locations by burning out the fuses at these locations using high-current pulses. Of course, this process is irreversible. PROMs provide flexibility and convenience not available with ROMs. The cost of preparing the masks needed for storing a particular information pattern makes ROMs cost effective only in large volumes. The alternative technology of PROMs provides a more convenient and considerably less expensive approach, because memory chips can be programmed directly by the user.

## EPROM

Another type of ROM chip provides an even higher level of convenience. It allows the stored data to be erased and new data to be written into it. Such an erasable, reprogrammable ROM is usually called an EPROM. It provides considerable flexibility during the development phase of digital systems. Since EPROMs are capable of retaining stored information for a long time, they can be used in place of ROMs or PROMs while software is being developed. In this way, memory changes and updates can be easily made. An EPROM cell has a structure similar to the ROM cell in Figure. However, the connection to ground at point P is made through a special transistor. The transistor is normally turned off, creating an open switch. It can be turned on by injecting charge into it that becomes trapped inside. Thus, an EPROM cell can be used to construct a memory in the same way as the previously discussed ROM cell. Erasure requires dissipating the charge trapped in the transistors that form the memory cells. This can be done by exposing the chip to ultraviolet light, which erases the entire contents of the chip. To make this possible, EPROM chips are mounted in packages that have transparent windows.

#### **EEPROM**

| An EPROM must be physically removed from the circuit for<br>reprogramming. Also, the stored information cannot be erased<br>selectively. The entire contents of the chip are erased when exposed to<br>ultraviolet light. Another type of erasable PROM can be programmed,<br>erased, and reprogrammed electrically. Such a chip is called an<br>electrically erasable PROM, or EEPROM. It does not have to be<br>removed for erasure. Moreover, it is possible to erase the cell contents<br>selectively. One disadvantage of EEPROMs is that different voltages<br>are needed for erasing, writing, and reading the stored data, which<br>increases circuit complexity. However, this disadvantage is outweighed<br>by the many advantages of EEPROMs. They have replaced EPROMs<br>in practice.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |     |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----|

| Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |     |     |

| An approach similar to EEPROM technology has given rise to flash<br>memory devices. A flash cell is based on a single transistor controlled<br>by trapped charge, much like an EEPROM cell. Also like an EEPROM,<br>it is possible to read the contents of a single cell. The key difference is<br>that, in a flash device, it is only possible to write an entire block of cells.<br>Prior to writing, the previous contents of the block are erased. Flash<br>devices have greater density, which leads to higher capacity and a lower<br>cost per bit. They require a single power supply voltage, and consume<br>less power in their operation. The low power consumption of flash<br>memories makes them attractive for use in portable, battery-powered<br>equipment. Typical applications include hand-held computers, cell<br>phones, digital cameras, and MP3 music players. In hand-held<br>computers and cell phones, a flash memory holds the software needed<br>to operate the equipment, thus obviating the need for a disk drive. A<br>flash memory is used in digital cameras to store picture data. In MP3<br>players, flash memories store the data that represent sound. Cell<br>phones, digital cameras, and MP3 players are good examples of<br>embedded systems. Single flash chips may not provide sufficient<br>storage capacity for the applications. Larger memory modules<br>consisting of a number of chips are used where needed. There are two<br>popular choices for the implementation of such modules: flash cards<br>and flash drive |    |     |     |

| (OR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |     |     |

| <ul> <li>D) Discuss DMA controller with block diagram.</li> <li>Blocks of data are often transferred between the main memory and I/O devices such as disks. This section discusses a technique for controlling such transfers without frequent, program-controlled intervention by the processor. The discussion concentrates on single-word or single-byte data transfers between the processor and I/O devices. Data are transferred from an I/O device to the memory by first reading them from the I/O device using an instruction such as Load R2, DATAIN</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13 | CO5 | REM |

| which loads the data into a processor register. Then, the data read are<br>stored into a memory location. The reverse process takes place for<br>transferring data from the memory to an I/O device. An instruction to<br>transfer input or output data is executed only after the processor<br>determines that the I/O device is ready, either by polling its status<br>register or by waiting for an interrupt request. In either case,<br>considerable overhead is incurred, because several program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |     |     |

instructions must be executed involving many memory accesses for each data word transferred. When transferring a block of data, instructions are needed to increment the memory address and keep track of the word count. The use of interrupts involves operating system routines which incur additional overhead to save and restore processor registers, the program counter, and other state information.

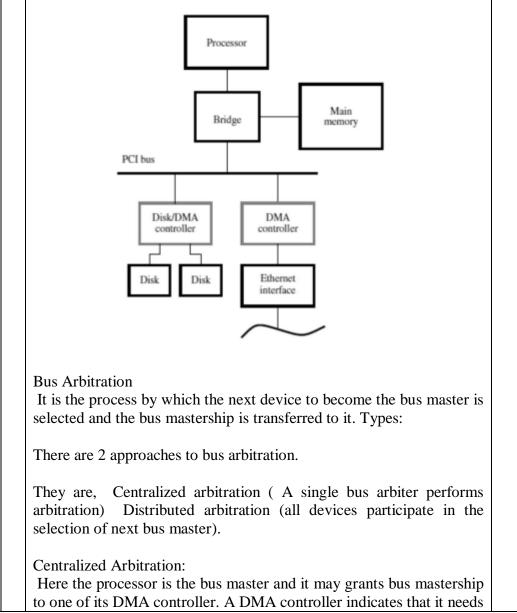

An alternative approach is used to transfer blocks of data directly between the main memory and I/O devices, such as disks. A special control unit is provided to manage the transfer, without continuous intervention by the processor. This approach is called direct memory access, or DMA. The unit that controls DMA transfers is referred to as a DMA controller. It may be part of the I/O device interface, or it may be a separate unit shared by a number of I/O devices. The DMA controller performs the functions that would normally be carried out by the processor when accessing the main memory. For each word transferred, it provides the memory address and generates all the control signals needed. It increments the memory address for successive words and keeps track of the number of transfers.

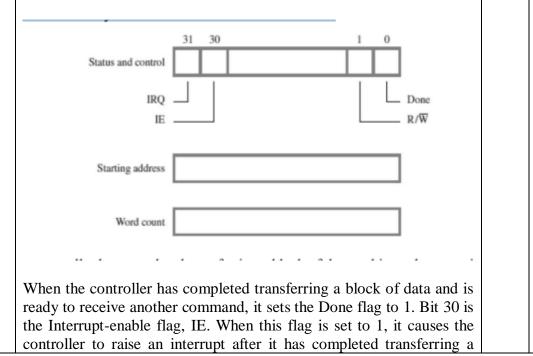

Although a DMA controller transfers data without intervention by the processor, its operation must be under the control of a program executed by the processor, usually an operating system routine. To initiate the transfer of a block of words, the processor sends to the DMA controller the starting address, the number of words in the block, and the direction of the transfer. The DMA controller then proceeds to perform the requested operation. When the entire block has been transferred, it informs the processor by raising an interrupt. Figure shows an example of the DMA controller registers that are accessed by the processor to initiate data transfer operations. Two registers are used for storing the starting address and the word count. The third register contains status and control flags. The R/W bit determines the direction of the transfer. When this bit is set to 1 by a program instruction, the controller performs a Read operation, that is, it transfers data from the memory to the I/O device. Otherwise, it performs a Write operation. Additional information is also transferred as may be required by the I/O device. For example, in the case of a disk, the processor provides the disk controller with information to identify where the data is located on the disk.

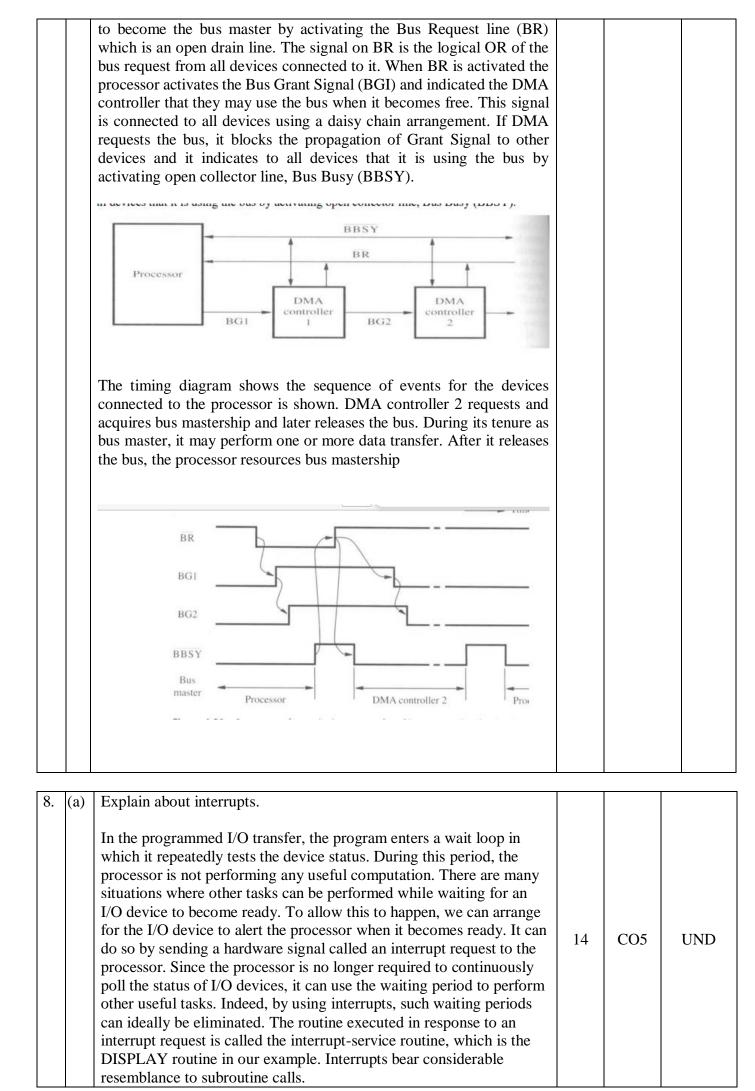

block of data. Finally, the controller sets the IRQ bit to 1 when it has requested an interrupt. Figure shows how DMA controllers may be used in a computer system such as that in Figure. One DMA controller connects a high-speed Ethernet to the computer's I/O bus (a PCI bus in the case of Figure). The disk controller, which controls two disks, also has DMA capability and provides two DMA channels. It can perform two independent DMA operations, as if each disk had its own DMA controller. The registers needed to store the memory address, the word count, and so on, are duplicated, so that one set can be used with each disk.

To start a DMA transfer of a block of data from the main memory to one of the disks, an OS routine writes the address and word count information into the registers of the disk controller. The DMA controller proceeds independently to implement the specified operation. When the transfer is completed, this fact is recorded in the status and control register of the DMA channel by setting the Done bit. At the same time, if the IE bit is set, the controller sends an interrupt request to the processor and sets the IRQ bit. The status register may also be used to record other information, such as whether the transfer took place correctly or errors occurred.

$Blooms \ Taxonomy: UND-Understand \ | \ REM-Remember \ | \ APP-Apply \ | \ ANA-Analyzing \ | \ EVA-Evaluate \ APP-Apply \ | \ ANA-Analyzing \ | \ EVA-Evaluate \ APP-Apply \ | \ ANA-Analyzing \ | \ EVA-Evaluate \ APP-Apply \ | \ ANA-Analyzing \ | \ EVA-Evaluate \ APP-Apply \ | \ ANA-Analyzing \ | \ EVA-Evaluate \ APP-Apply \ | \ ANA-Analyzing \ | \ EVA-Evaluate \ APP-Apply \ | \ ANA-Analyzing \ | \ EVA-Evaluate \ APP-Apply \ | \ ANA-Analyzing \ | \ EVA-Evaluate \ APP-Apply \ | \ APP-Apply \ | \ ANA-Analyzing \ | \ EVA-Evaluate \ APP-Apply \ | \ APA-Analyzing \ | \ EVA-Evaluate \ APP-Apply \ | \ APA-Analyzing \ | \ APA-Analyzing \ | \ APA-Analyzing \ | \ APA-Apply \ | \ APA-Analyzing \ | \ APA-Analyzing \ | \ APA-Analyzing \ | \ APA-Apply \ | \ APA-Analyzing \ | \ APA-Analyzing \ | \ APA-Analyzing \ | \ APA-Apply \ | \$

Assume that an interrupt request arrives during execution of instruction i in Figure. The processor first completes execution of instruction i. Then, it loads the program counter with the address of the first instruction of the interrupt-service routine. For the time being, let us assume that this address is hardwired in the processor. After execution of the interrupt-service routine, the processor returns to instruction i + 1. Therefore, when an interrupt occurs, the current contents of the PC, which point to instruction i + 1, must be put in temporary storage in a known location. A Return-from-interrupt instruction at the end of the interrupt-service routine reloads the PC from that temporary storage location, causing execution to resume at instruction i + 1. The return address must be saved either in a designated general-purpose register or on the processor stack.

We should note that as part of handling interrupts, the processor must inform the device that its request has been recognized so that it may remove its interrupt-request signal. This can be accomplished by means of a special control signal, called interrupt acknowledge, which is sent to the device through the interconnection network. An alternative is to have the transfer of data between the processor and the I/O device interface accomplish the same purpose. The execution of an instruction in the interrupt-service routine that accesses the status or data register in the device interface implicitly informs the device that its interrupt request has been recognized.

So far, treatment of an interrupt-service routine is very similar to that of a subroutine. An important departure from this similarity should be noted. A subroutine performs a function required by the program from which it is called. As such, potential changes to status information and contents of registers are anticipated. However, an interrupt-service routine may not have any relation to the portion of the program being executed at the time the interrupt request is received. Therefore, before starting execution of the interrupt service routine, status information and contents of processor registers that may be altered in unanticipated ways during the execution of that routine must be saved. This saved information must be restored before execution of the interrupted program is resumed. In this way, the original program can continue execution without being affected in any way by the interruption, except for the time delay.

The task of saving and restoring information can be done automatically by the processor or by program instructions. Most modern processors save only the minimum amount of information needed to maintain the integrity of program execution. This is because the process of saving and restoring registers involves memory transfers that increase the total execution time, and hence represent execution overhead. Saving registers also increases the delay between the time an interrupt request is received and the start of execution of the interruptservice routine. This delay is called interrupt latency. In some applications, a long interrupt latency is unacceptable. For these reasons, the amount of information saved automatically by the processor when an interrupt request is accepted should be kept to a minimum. Typically, the processor saves only the contents of the program counter and the processor status register. Any additional information that needs to be saved must be saved by explicit instructions at the beginning of the interrupt-service routine and restored at the end of the routine. In some earlier processors, particularly those with a small number of registers, all registers are saved automatically by the processor hardware at the time an interrupt request is accepted. The data saved are restored to their respective registers as part of the execution of the Returnfrominterrupt instruction.

Some computers provide two types of interrupts. One saves all register contents, and the other does not. A particular I/O device may use either type, depending upon its response time requirements. Another interesting approach is to provide duplicate sets of processor registers. In this case, a different set of registers can be used by the interruptservice routine, thus eliminating the need to save and restore registers. The duplicate registers are sometimes called the shadow registers. An interrupt is more than a simple mechanism for coordinating I/O transfers. In a general sense, interrupts enable transfer of control from one program to another to be initiated by an event external to the computer. Execution of the interrupted program resumes after the execution of the interrupt-service routine has been completed. The concept of interrupts is used in operating systems and in many control applications where processing of certain routines must be accurately timed relative to external events. The latter type of application is referred to as real-time processing.

#### **Enabling and Disabling Interrupts**

The facilities provided in a computer must give the programmer complete control over the events that take place during program execution. The arrival of an interrupt request from an external device causes the processor to suspend the execution of one program and start the execution of another. Because interrupts can arrive at any time, they may alter the sequence of events from that envisaged by the programmer. Hence, the interruption of program execution must be carefully controlled. A fundamental facility found in all computers is the ability to enable and disable such interruptions as desired.

There are many situations in which the processor should ignore interrupt requests. For instance, the timer circuit should raise interrupt requests only when the COMPUTE routine is being executed. It should be prevented from doing so when some other task is being performed. In another case, it may be necessary to guarantee that a particular sequence of instructions is executed to the end without interruption because the interrupt-service routine may change some of the data used by the instructions in question. For these reasons, some means for enabling and disabling interrupts must be available to the programmer.

It is convenient to be able to enable and disable interrupts at both the processor and I/O device ends. The processor can either accept or ignore interrupt requests. An I/O device can either be allowed to raise interrupt requests or prevented from doing so. A commonly used mechanism to achieve this is to use some control bits in registers that can be accessed by program instructions. The processor has a status register (PS), which contains information about its current state of

|     | operation. Let one bit, IE, of this register be assigned for<br>enabling/disabling interrupts. Then, the programmer can set or clear IE<br>to cause the desired action. When IE = 1, interrupt requests from I/O<br>devices are accepted and serviced by the processor. When IE = 0, the<br>processor simply ignores all interrupt requests from I/O devices. The<br>interface of an I/O device includes a control register that contains the<br>information that governs the mode of operation of the device. One bit<br>in this register may be dedicated to interrupt control. The I/O device is<br>allowed to raise interrupt requests only when this bit is set to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |     |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|-----|

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |     |     |

| (b) | Summarize in detail about synchronous and asynchronous bus<br>The I/O interface of a device consists of the circuitry needed to<br>connect that device to the bus. On one side of the interface are the bus<br>lines for address, data, and control. On the other side are the<br>connections needed to transfer data between the interface and the I/O<br>device. This side is called a port, and it can be either a parallel or a<br>serial port. A parallel port transfers multiple bits of data<br>simultaneously to or from the device. A serial port sends and receives<br>data one bit at a time. Communication with the processor is the same<br>for both formats; the conversion from a parallel to a serial format and<br>vice versa takes place inside the interface circuit.<br>With double buffering, the transfer of the second character can begin as<br>soon as the first character is loaded from the shift register into the DAT<br>IN register. Thus, provided the processor reads the contents of<br>DATAIN before the serial transfer of the second character is<br>completed, the interface can receive a continuous stream of input data<br>over the serial line. An analogous situation occurs in the output path of<br>the interface. During serial transmission, the receiver needs to know<br>when to shift each bit into its input shift register. Since there is no<br>separate line to carry a clock signal from the transmitter to the receiver,<br>the timing information needed must be embedded into the transmitted<br>data using an encoding scheme. There are two basic approaches. The<br>first is known as asynchronous transmission, because the receiver uses<br>a clock that is not synchronized with the transmitter clock. In the<br>second approach, the receiver is able to generate a clock that is<br>synchronous<br>This approach uses a technique called start-stop transmission. Data are<br>organized in small groups of 6 to 8 bits, with a well-defined beginning<br>and end. In a typical arrangement, alphanumeric characters encoded in<br>8 bits are transmitted as shown in Figure. The line connecting the<br>transmitter and the receiver is in the 1 state | 14 | CO5 | UND |

| the incoming data as close to the center of each bit as possible. It does<br>so by using a clock signal whose frequency, fR, is substantially higher<br>than the transmission clock, fT . Typically, fR = 16fT . This means that<br>16 pulses of the local clock occur during each data bit interval. This<br>clock is used to increment a modulo-16 counter, which is cleared to 0<br>when the leading edge of a Start bit is detected. The middle of the Start<br>bit is reached at the count of 8. The state of the input line is sampled<br>again at this point to confirm that it is a valid Start bit (a zero), and the<br>counter is cleared to 0. From this point onward, the incoming data signal<br>is sampled whenever the count reaches 16, which should be close to the<br>middle of each incoming bit. Therefore, as long as fR/16 is sufficiently<br>close to fT , the receiver will correctly load the bits of the incoming<br>character.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Synchronous Transmission<br>In the start-stop scheme described above, the position of the 1-to-0<br>transition at the beginning of the start bit in Figure is the key to obtaining<br>correct timing information. This scheme is useful only where the speed<br>of transmission is sufficiently low and the conditions on the<br>transmission link are such that the square waveforms shown in the figure<br>maintain their shape. For higher speed a more reliable method is needed<br>for the receiver to recover the timing information. In synchronous<br>transmission, the receiver generates a clock that is synchronized to that<br>of the transmitter by observing successive 1-to-0 and 0-to-1 transitions<br>in the received signal. It adjusts the position of the active edge of the<br>clock to be in the center of the bit position.<br>A variety of encoding schemes are used to ensure that enough signal<br>transitions occur to enable the receiver to generate a synchronized clock<br>and to maintain synchronization. Once synchronization is achieved, data<br>transmission can continue indefinitely. Encoded data are usually<br>transmitted in large blocks consisting of several hundreds or several<br>thousands of bits. The beginning and end of each block are marked by<br>appropriate codes, and data within a block are organized according to<br>an agreed upon set of rules. Synchronous transmission enables very high<br>data transfer rates . |  |  |

**Prepared By**

Verified By

HOD