## SNS COLLEGE OF TECHNOLOGY

Coimbatore-35

An Autonomous Institution

Accredited by NBA – AICTE and Accredited by NAAC – UGC with 'A+' Grade Approved by AICTE, New Delhi & Affiliated to Anna University, Chennai

# DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

#### 19ECB211 - MICROCONTROLLER PROGRAMMING & INTERFACING

II YEAR IV SEM

UNIT V- ADVANCED MICROCONTROLLERS

TOPIC 5 – ARM Architecture

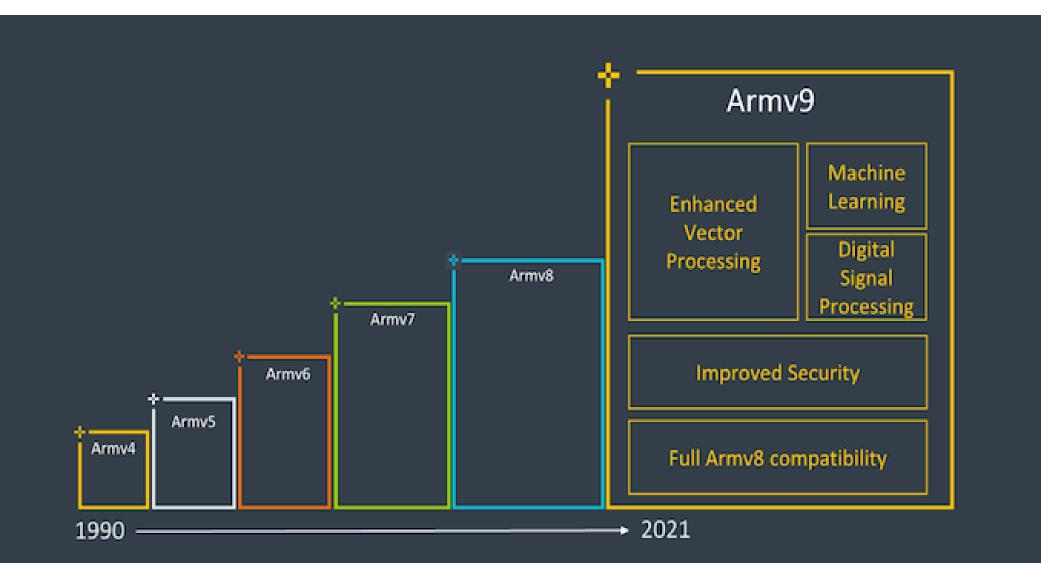

- > The Arm architecture is the keystone of the world's largest compute ecosystem.

- It enables our partners to build their products in an efficient, affordable, and secure way.

- Arm's proven track record of delivering world-class architecture designs is reflected in the success of this diverse and ever-evolving ecosystem.

- Arm's architecture specifications are licensed by partners, who create compliant silicon chips based on them.

- ➤ With more than 125 billion devices containing Arm-based chips, our architecture empowers innovation in multiple markets enabling partner innovation

- The Arm architecture is a family of reduced instruction set computing (RISC) architectures for computer processors.

- ➤ It is the most pervasive processor architecture in the world, with billions of Armbased devices shipped every year, from sensors, wearables and smartphones to supercomputers.

Benefits of the Arm CPU architecture include:

- Integrated security

- High performance and energy efficiency

- > Large ecosystem for global support

- Pervasive across markets and locations

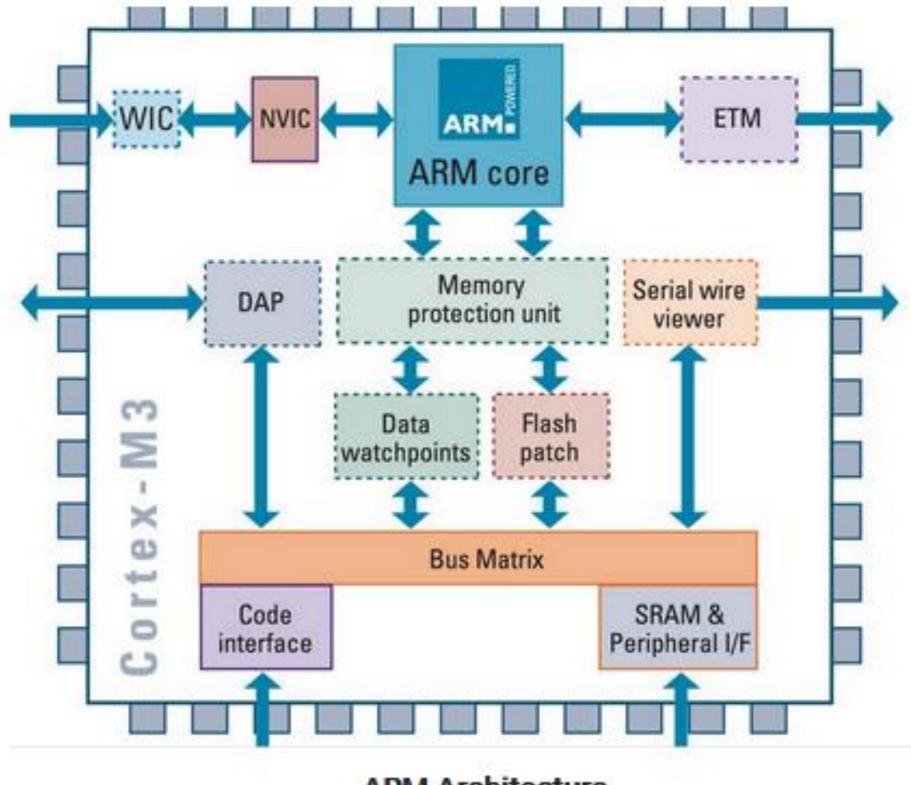

**ARM Architecture**

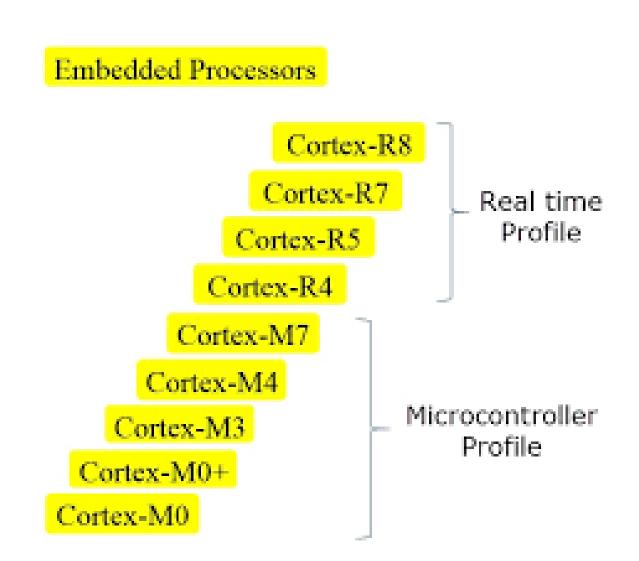

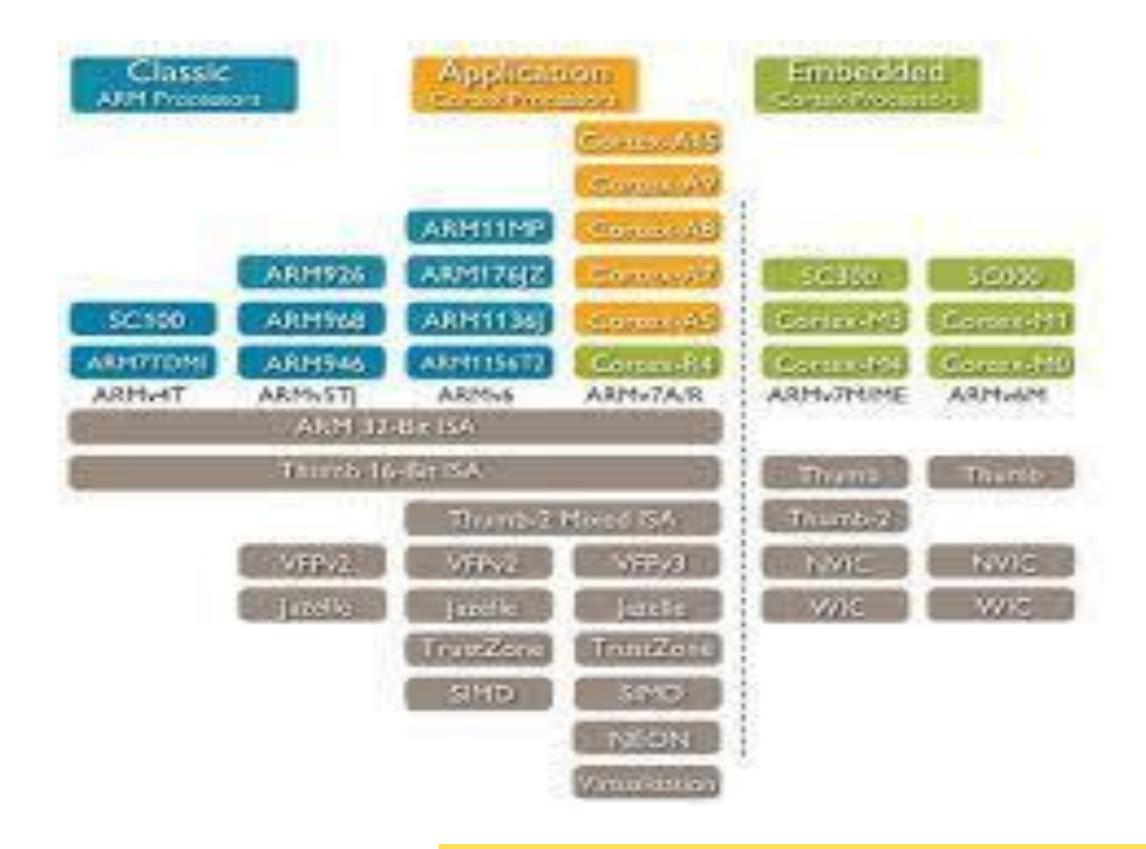

➤ The ARM cortex is a complicated microcontroller within the ARM family that has ARMv7 design. There are 3 subfamilies within the ARM cortex family:

ARM Cortex Ax-series

ARM-Cortex Rx-series

ARM-Cortex Mx-series

## Which Architecture is my processor?

#### **Data Sizes and Instruction Sets**

- 1.Arm is a RISC Processor

- 2.ARM is a 32 bit load store architecture

- 3.Most internal registers are 32 bits

With relation to Arm,

Word = 32 bits

Halfword = 16 bits

Doubleword = 64 bits

4.Implements two instruction sets – Arm and Thumb Instructions

5.Older cores support 16 bit thumb instruction only.

Maintains code density with increased feasibility.

## **Processor Modes - A and R**

| Processor mode |     | Description                                            |  |

|----------------|-----|--------------------------------------------------------|--|

| User           | usr | Normal program execution mode                          |  |

| FIQ            | fiq | Supports a high-speed data transfer or channel process |  |

| IRQ            | irq | Used for general-purpose interrupt handling            |  |

| Supervisor     | svc | A protected mode for the operating system              |  |

| Abort          | abt | Implements virtual memory and/or memory protection     |  |

| Undefined      | und | Supports software emulation of hardware coprocessor    |  |

| System         | sys | Runs privileged operating system tasks                 |  |

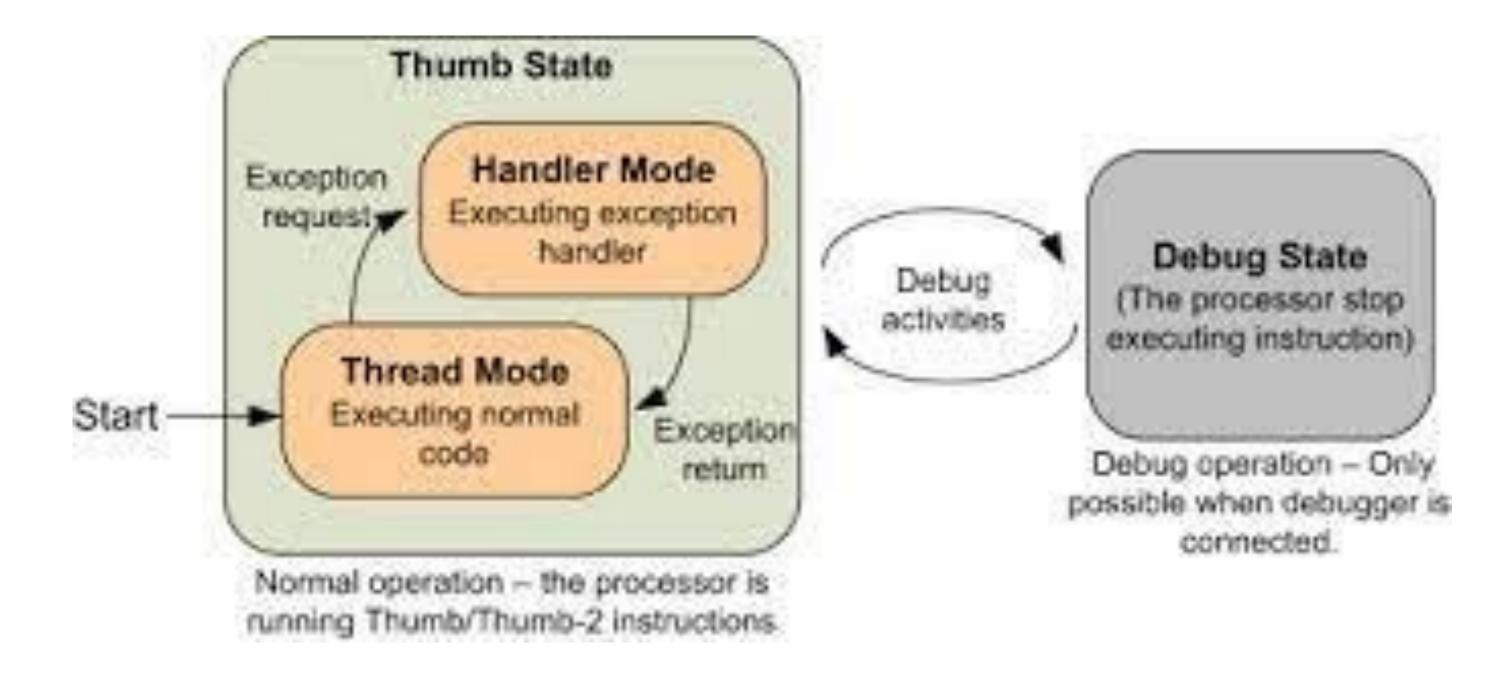

## **Processor Modes - Cortex M**

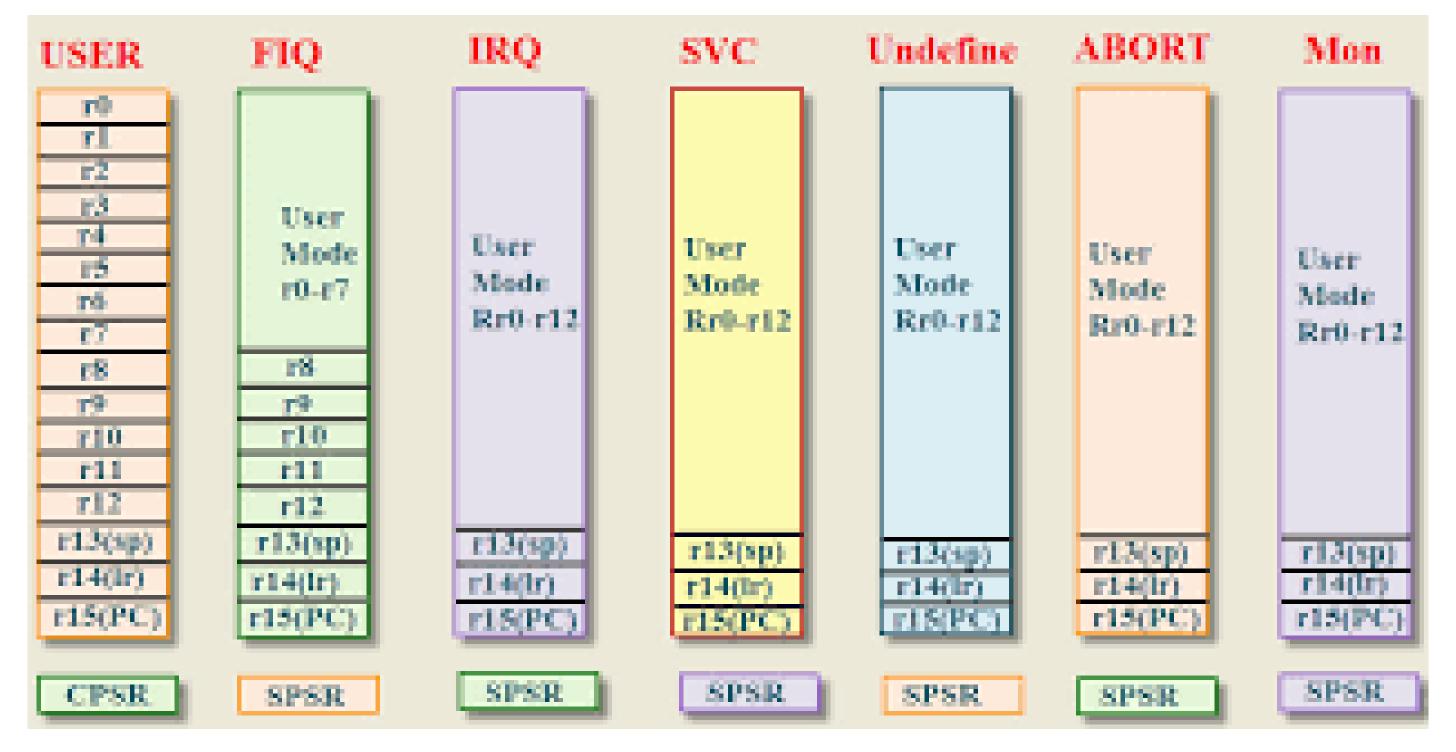

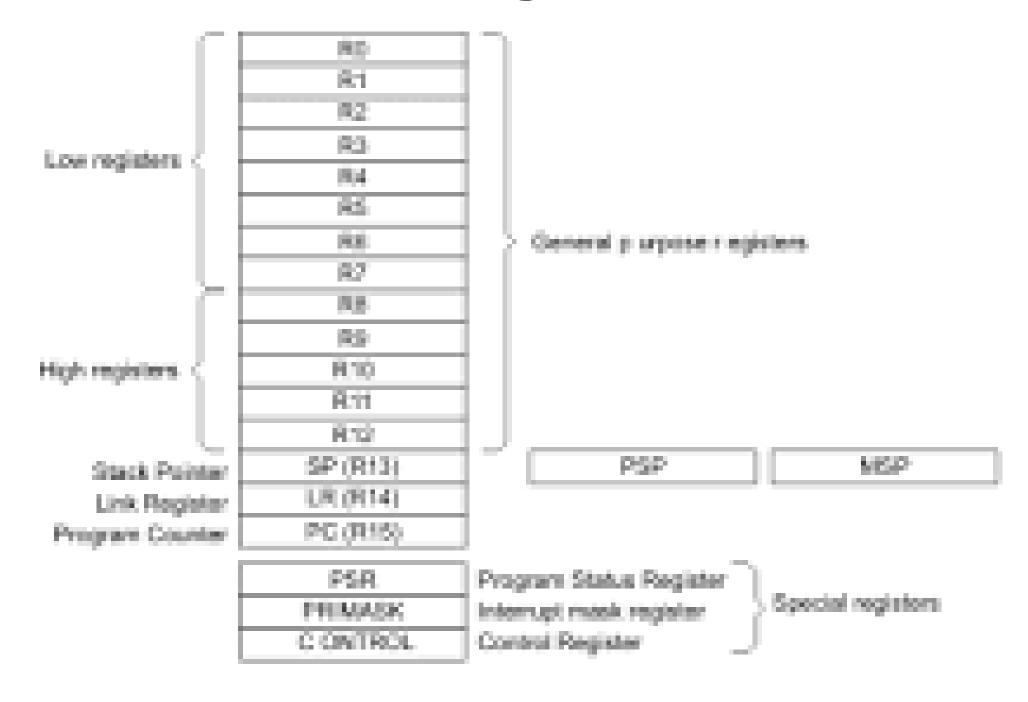

## **ARM Register Set - A and R**

# ARM Register Set - A and R

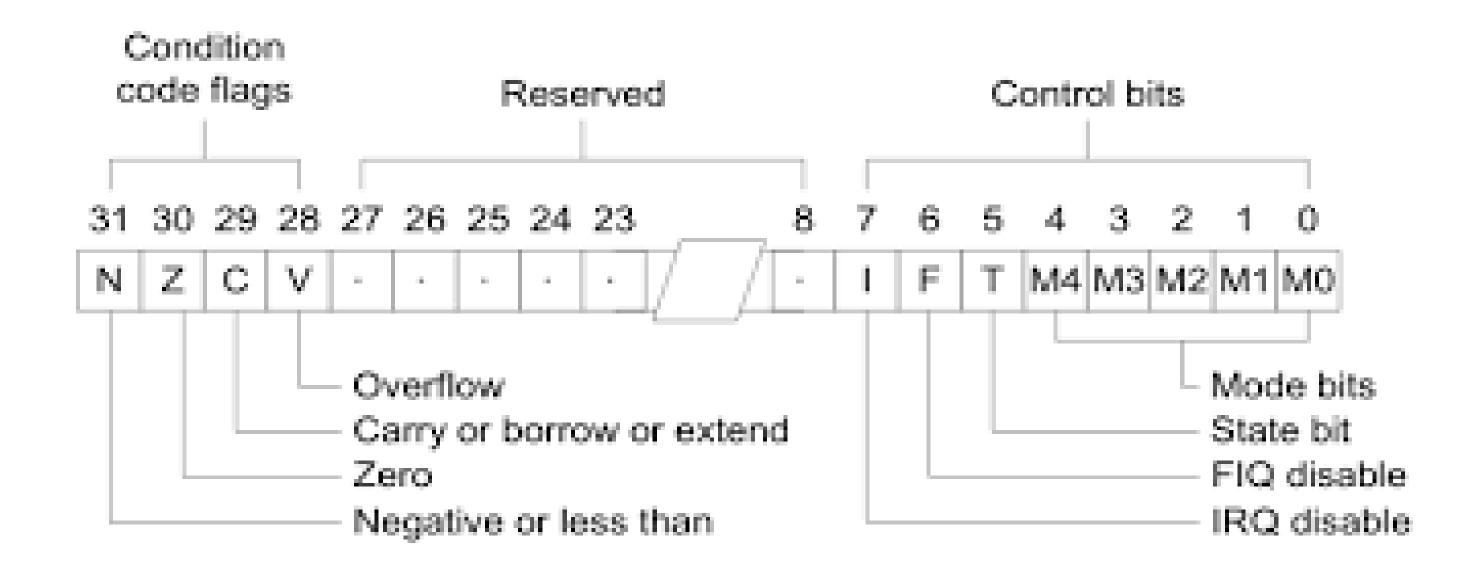

#### ARM PROGRAM STATUS REGISTER

## **ARM EXCEPTIONS**

| Exception type                                  | Mode       | Normal<br>address | High vector address |

|-------------------------------------------------|------------|-------------------|---------------------|

| Reset                                           | Supervisor | 0x00000000        | 0xFFFF0000          |

| Undefined instructions                          | Undefined  | 0x00000004        | 0xFFFF0004          |

| Software interrupt (SWI)                        | Supervisor | 0x00000008        | 0xFFFF0008          |

| Prefetch Abort (instruction fetch memory abort) | Abort      | 0x000000C         | 0xFFFF000C          |

| Data Abort (data access memory abort)           | Abort      | 0x00000010        | 0xFFFF0010          |

| IRQ (interrupt)                                 | IRQ        | 0x00000018        | 0xFFFF0018          |

| FIQ (fast interrupt)                            | FIQ        | 0x0000001C        | 0xFFFF001C          |

#### The ARM Architecture

- ➤ Arithmetic Logic Unit

- > Booth multiplier

- Barrel shifter

- > Control unit

- Register file

#### **Arithmetic Logic Unit (ALU)**

The ALU has two 32-bits inputs.

The primary comes from the register file, whereas the other comes from the shifter. Status registers flags modified by the ALU outputs.

## References

https://www.ti.com/sc/docs/products/micro/msp430/userguid/ag\_02.pdf

https://unacademy.com/lesson/architecture-of-msp430-microcontroller/B3AQZF86

https://binaryupdates.com/bitwise-operations-in-embedded-programming/

John H Davies, MSP430 Microcontroller Basics, Newnes Publications, Elsevier, 2008.